As you know I'm working on some next generation hardware as described here: https://sebiik.github.io/community.axoloti.com.backup/t/next-gen-and-mini-axoloti-hardware-discussion/5908/216

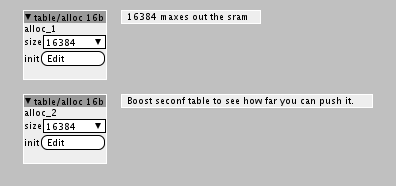

I want to compile a nice collection of patches that really push the hardware for performance testing. I'm specifically interested in patches that expose issues with SD Card locking or stuttering. Patches that run into memory limitations either SRAM or SDRAM will also be useful.

These can be patches that you have from the past or new patches you can make quickly to illustrate unexpected behavior.

Think of anything that can break or crash the current system, any situation where you noticed issues or were confused by something. Even if you have a patch that is only unstable some of the time or under certain circumstances, submit it and describe what happened.

As we go forward I want us to get in the habit of creating minimal test patches that expose specific issues. Try to give me the smallest possible patch that exposes the issue even if it came from some larger project you were working on. That will make it easier for me to resolve. This might be the single biggest way to contribute if you're not comfortable working on the internals: find bugs or issues, create minimal test patches that illustrate them. This makes it a lot easier for other developers to come in and fix issues too.

By the way, this thread should be specific to particular patches and firmware behavior, we'll deal with overall patcher issues separately.