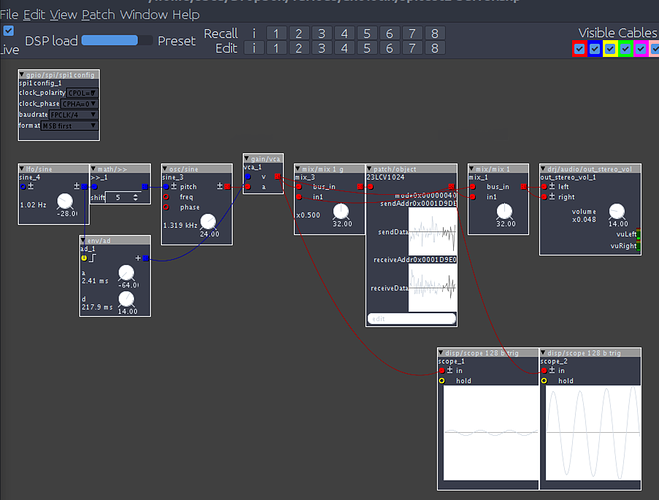

So I've been playing around trying to get a 23LC1024 SPI SRAM chip working with Axoloti running on the STM32F407 Discovery board.

I know I know, why try using SPI SRAM when the stock Axoloti board has fast and abundant SDRAM. I do own a stock Axoloti and use it live, and my playing with the Discovery board is mainly for learning purposes. Kindly see below what I've got so far...

Although the code is still quite ineffective the problem is, the SPI read and write actions seem to be using up so much CPU. Does anyone have a hint on what I am missing (something about threads? Maybe use spiExchange instead of spiSend/spiReceive?)

I did try minimizing redundant function calls and do the whole read write action in k-rate, writing to the frac32[i] buffer in a 'for' loop, but it ended up in roughly the same CPU load.

I am using SPI1 (used SPI2 before, same)

Or is that the best SPI can do on ChibiOS / Axoloti / Discovery? I dare doubt that since the 23LC1024 SRAM works fast (?) and clean e.g. on Teensy 3.X with the Teensy Audio Library?

This is my custom SPI config object code in XML (or download file below):

https://pastebin.com/wNzuyYzV

And here's the 23LC(V)1024 delay test object code in XML (or download file below):

https://pastebin.com/WT9dbQdU

spi1config.axo (3.2 KB)

spitest2-buffer.axp (10.6 KB)

Thanks in advance, and please do let me know wherever my code sucks!